### Logical Time @ work: the RT-Simex project

#### Julien DeAntoni, Frédéric Mallet, Charles André I3S/UNS/INRIA

#### Frédéric Thomas Obeo

#### SAFA 2010

### Logical Time @ work: the RT-Simex project

#### Julien DeAntoni, Frédéric Mallet, I3S/UNS/INRIA

#### Frédéric Thomas Obeo

#### SAFA 2010

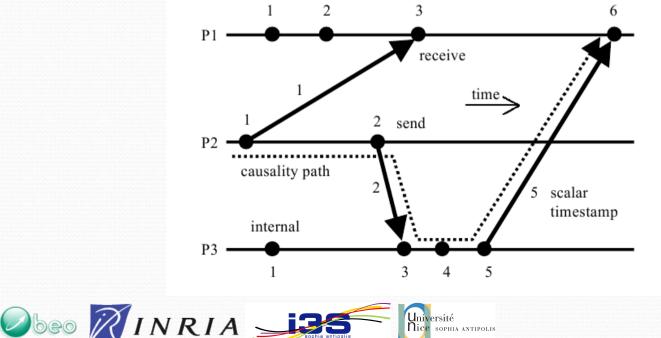

## Logical Time...

- focuses on causal relations between events

- Is independent of the abstraction level

- Is multi-clock (polychronous)

- Provides a partial order between events

After 23 starts of the computer, a disk check is done

The computation duration is 156 processor ticks

## Logical Time...

- focuses on causal relations between events

- Is independent of the abstraction level

- Is multi-clock (polychronous)

- Provides a partial order between events

After 23 starts of the computer, a disk check is done

The computation duration is 156 processor ticks

In modern laptop, tick is logical since the processor speed depend on the battery level

## Logical Time...

- focuses on causal relations between events

- Is independent of the abstraction level

- Is multi-clock (polychronous)

- Provides a partial order between events

rsité

SOPHIA ANTIPOLIS

LOGICAL TIME Friedemann Mattern Darmstadt University of Technology

## Physical time Time...

Can be seen as a special case of logical time

After 5 secondes, it stops...  $\cong$ After 5 events of the "second" clock, it stops

Logical Time @ work: the RT-Simex project

#### Julien DeAntoni, Frédéric Mallet, I3S/UNS/INRIA

#### Frédéric Thomas Obeo

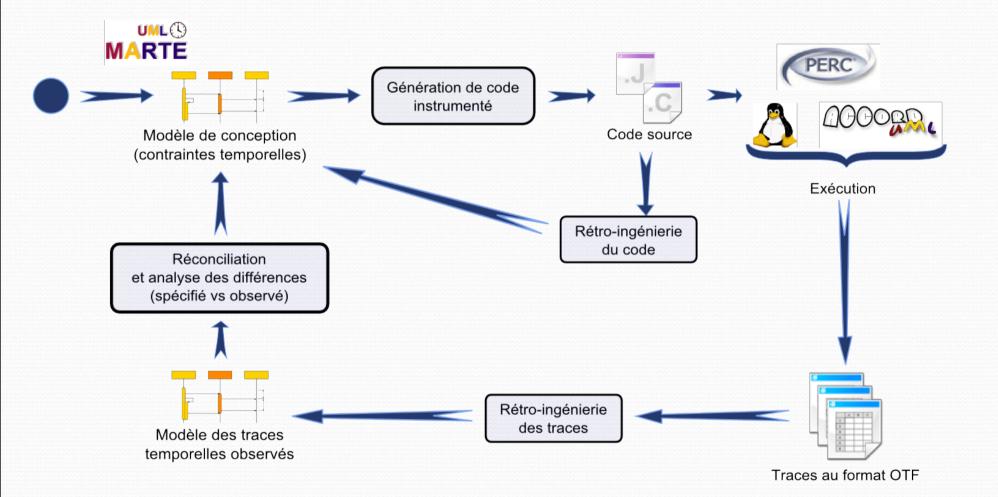

#### Retro-ingénierie de Traces d'analyse de SIMulation et d'EXécution de systèmes temps-réel

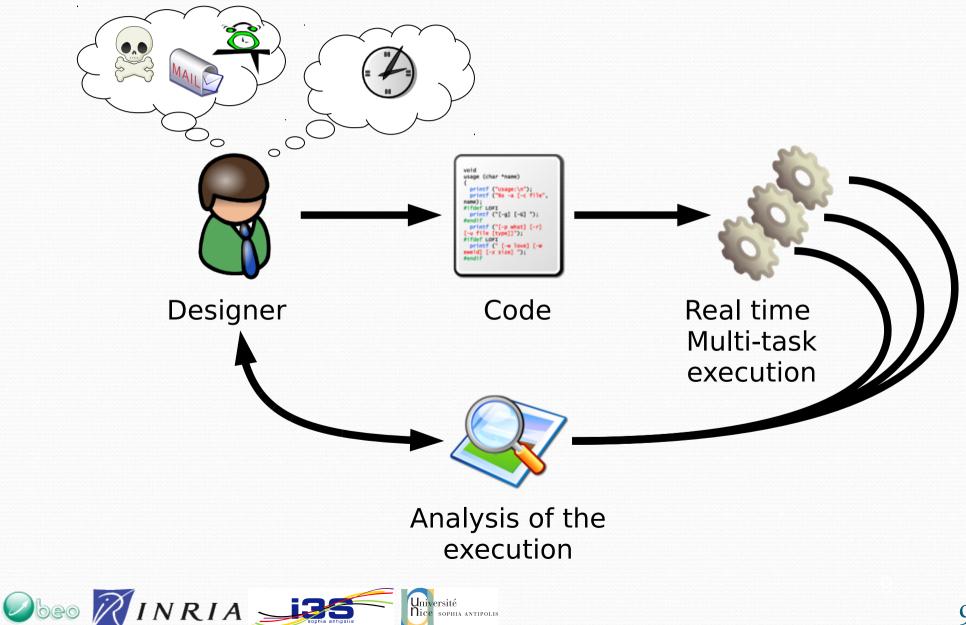

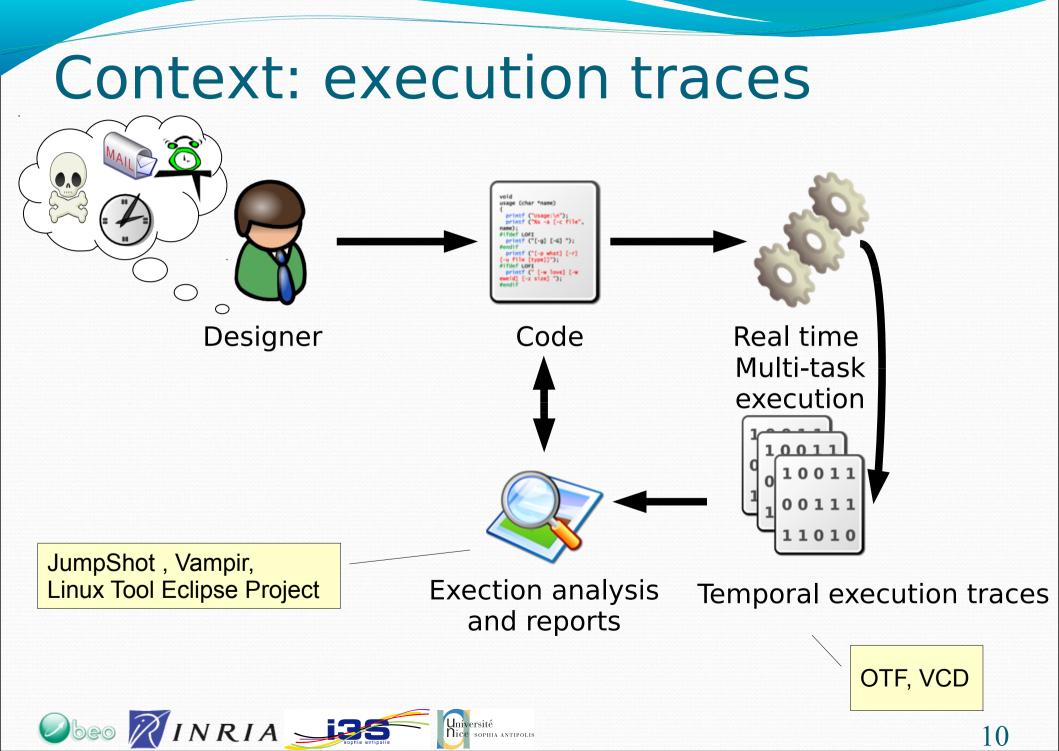

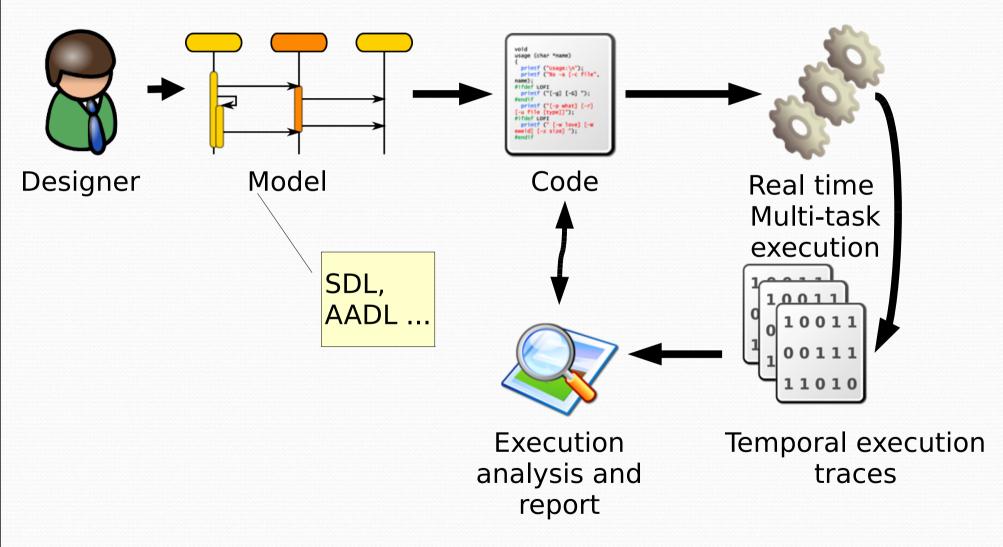

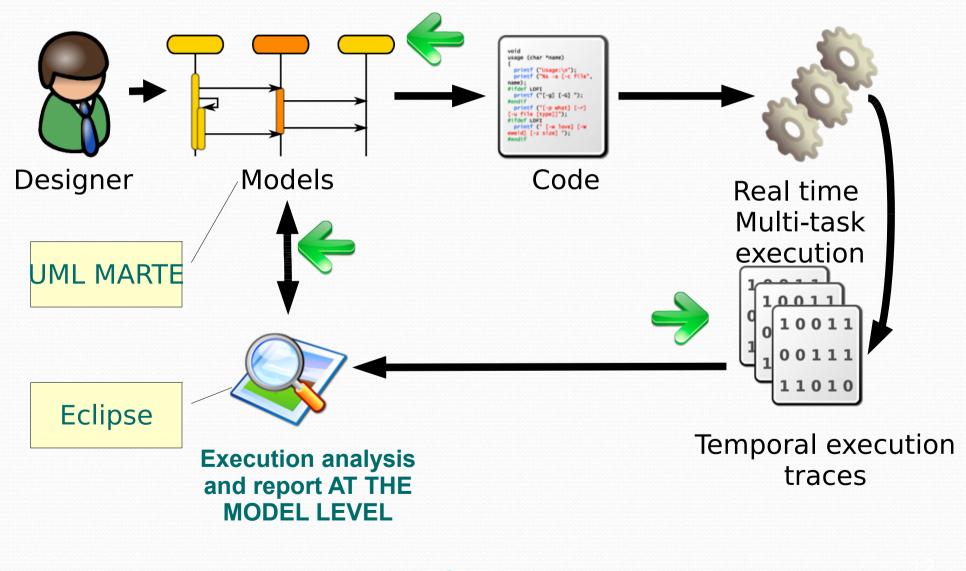

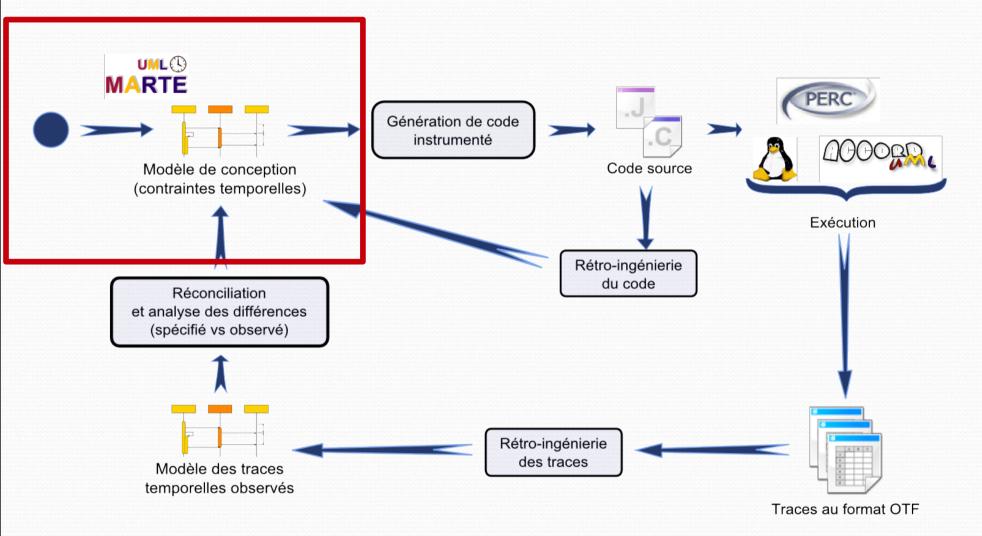

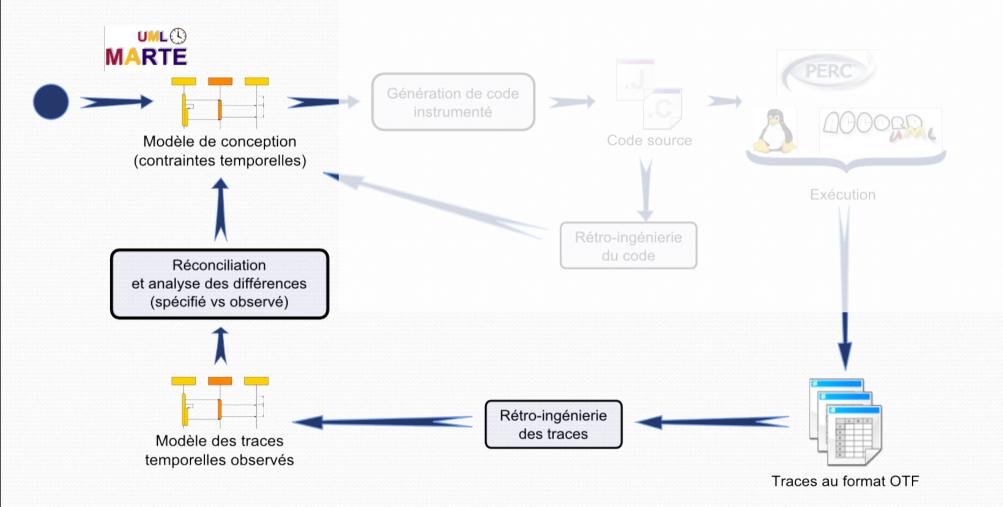

## Context : help the designer

### observations

11

## **RT-Simex objectives**

Obeo RINRIA Supersité Université

Obeo WINRIA STREAM

## Logical Time @ work: the **RT-Simex** project

#### Julien DeAntoni, Frédéric Mallet, I3S/UNS/INRIA

#### Frédéric Thomas Obeo

#### SAFA 2010

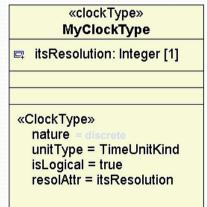

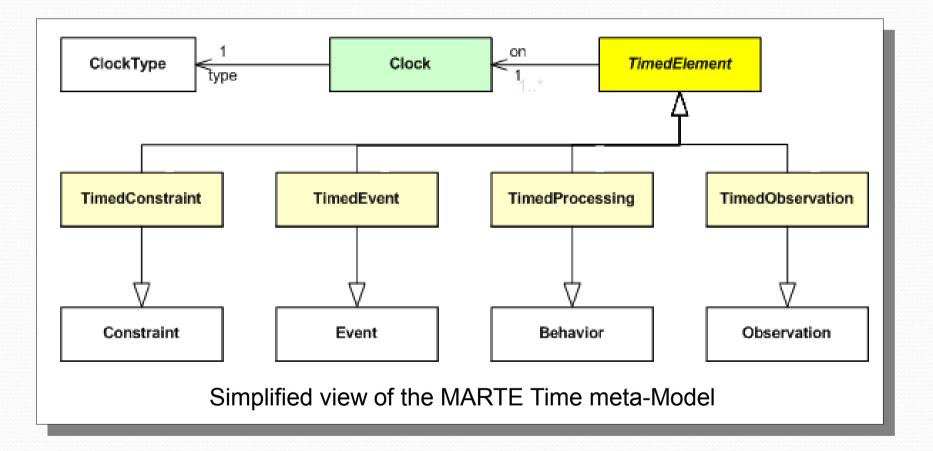

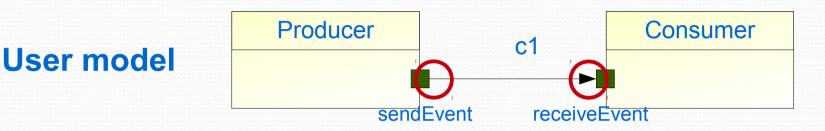

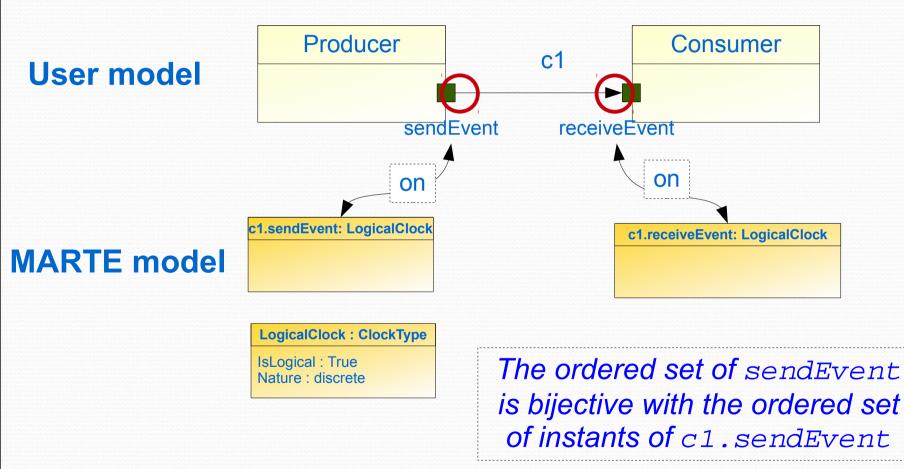

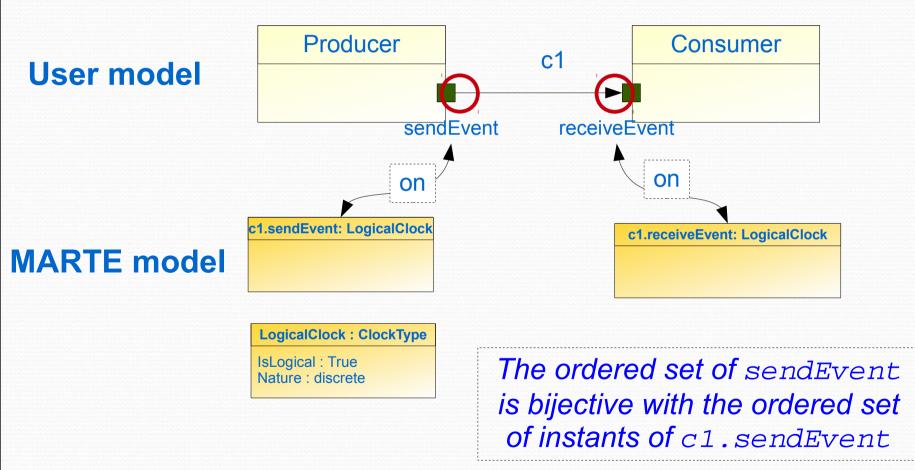

- SubProfile of the MARTE UML profile standardized by the OMG (Object Management Group)

- Reviewed and accepted by the community

- Implemented in Papyrus, magic draw, etc

- Under Implementation in other UML tools

- A Domain Model integrated with eclipse and usable with Domain Specific Language

- The main concept is the **Clock**.

- It is a way to specify a, possibly infinite, ordered set of instants

- It can be logical or chronometric, discrete or dense

- Its type is a ClockType

|                           | «clock»  |

|---------------------------|----------|

| itsClock: MyClockType [1] |          |

| itsResolution = 1         |          |

| «Clock»                   |          |

| standard = 1              |          |

| type = MyC                | lockType |

| unit = tick               |          |

#### • Sketchy example of its use

• Sketchy example of its use

## • Sketchy example of its use

#### Sketchy example of its use

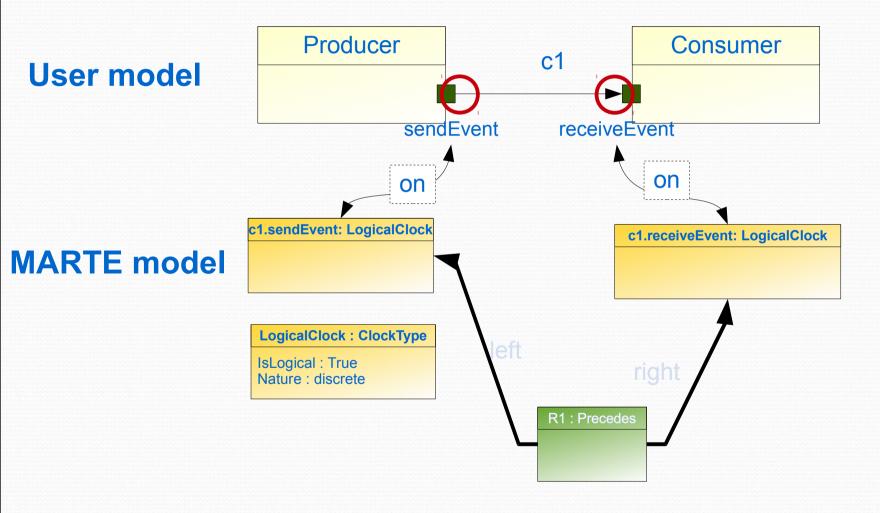

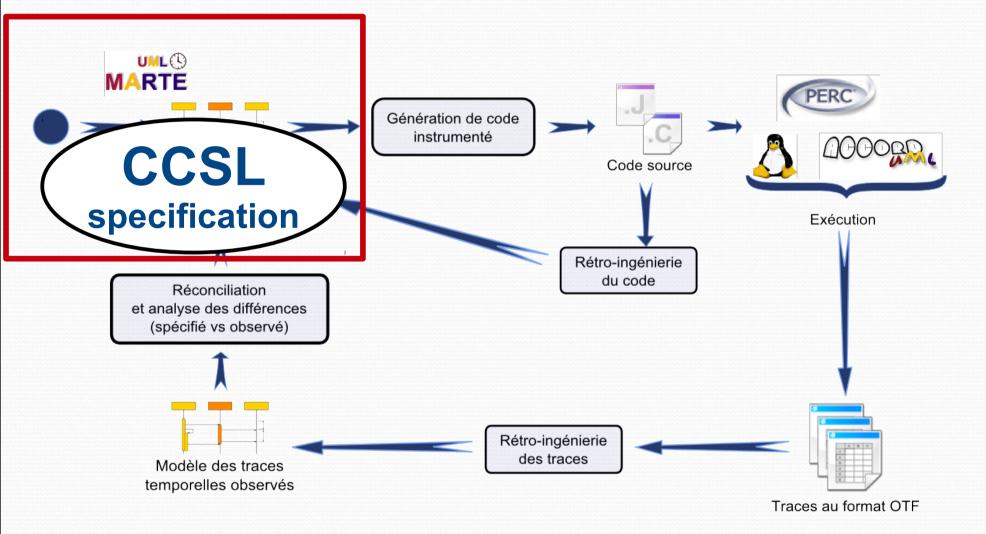

## CCSL

- Clock Constraint Specification Language

- Firstly introduced in the MARTE TIME profile

- Declarative model-based language integrated with Eclipse

- Formal semantics (both denotational and operational)

- Tooled (TimeSquare)

- → Explicitly represents / specifies relations between clocks

CCSL (Clock Constraint Specification Language)

#### Relations: dependencies between clocks

- Coincidence

- Exclusion  $\rightarrow$  #

- Precedence  $\rightarrow$  <

- Alternance

- Expressions: a mean to create new clocks from others

- Delay

Union

- → **delayedFor** X **on** aClock Filtering → aClock filteredBy aBinaryWord

- $\rightarrow$  aClock **union** anotherClock

- Intersection  $\rightarrow$  aClock inter anotherClock

- Periodicity → periodicOn aClock period X offset Y

Obeo RINRIA

...

CCSL (Clock Constraint Specification Language)

#### - Relations: dependencies between clocks

- Coincidence

- Exclusion → **#**

- Precedence  $\rightarrow$  <

- Alternance  $\rightarrow$  ~

- Expressions: a mean to create new clocks from others

- Delay

- → delayedFor X on aClock

- Filtering → aClock filteredBy aBinaryWord

- Union

Obeo RINRIA -

- → aClock **union** anotherClock • Intersection → aClock **inter** anotherClock

- Periodicity → periodicOn aClock period X offset Y

- Libraries: user-defined relations and expressions

# • Sketchy example of its use

# • Sketchy example of its use

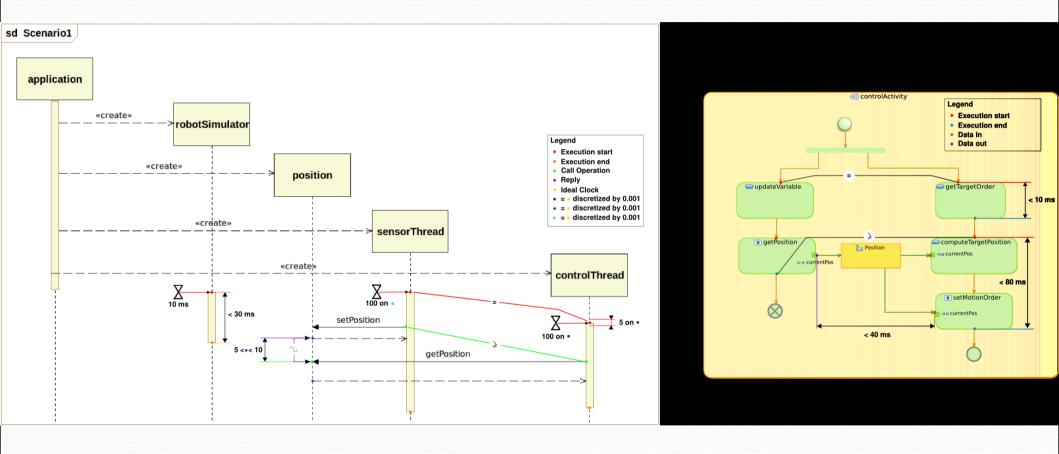

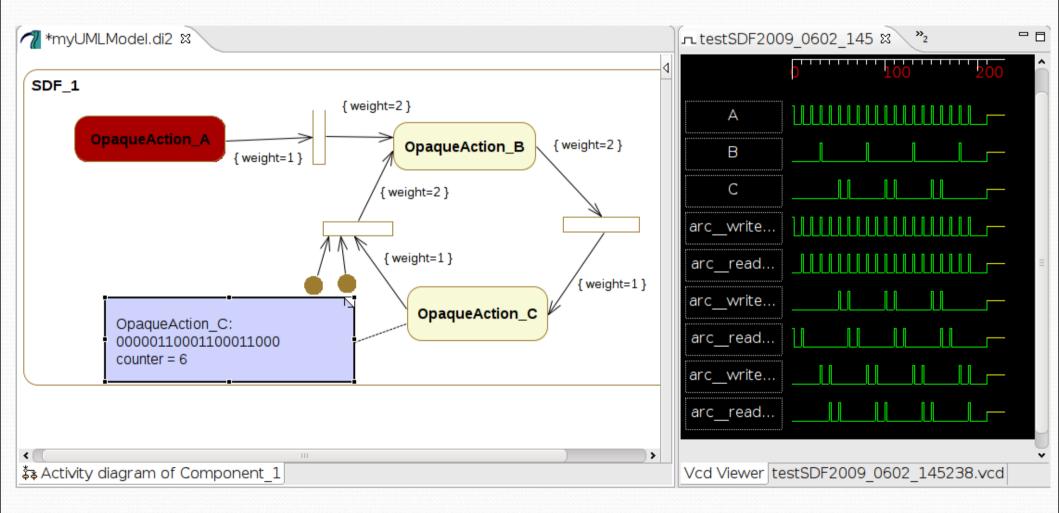

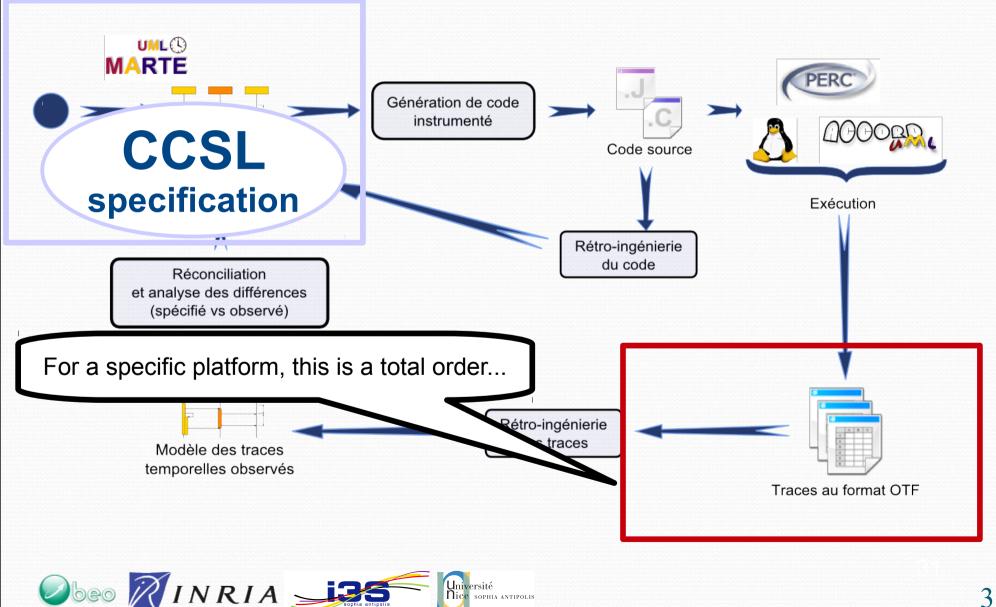

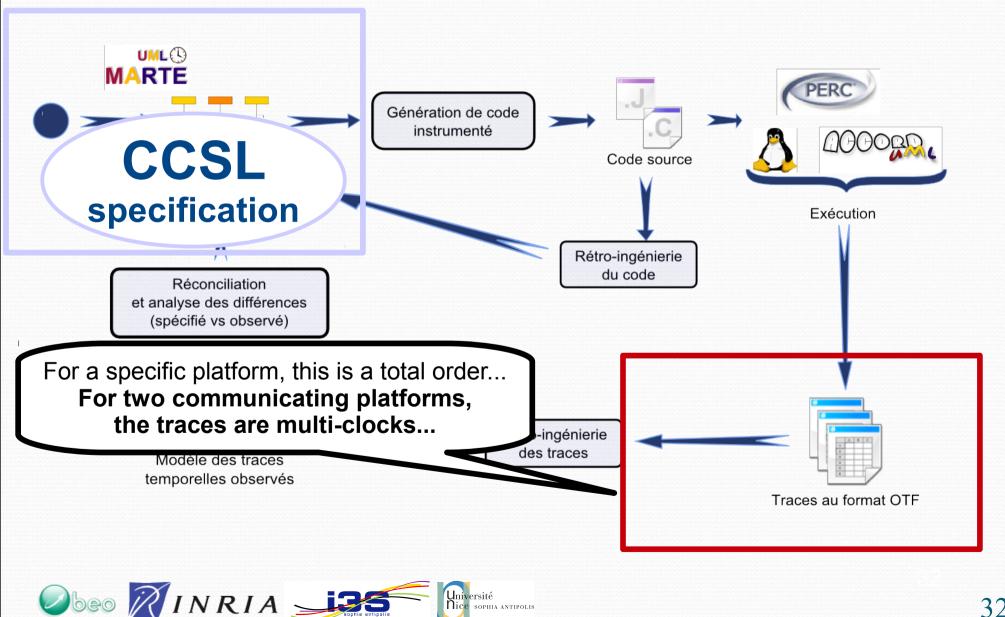

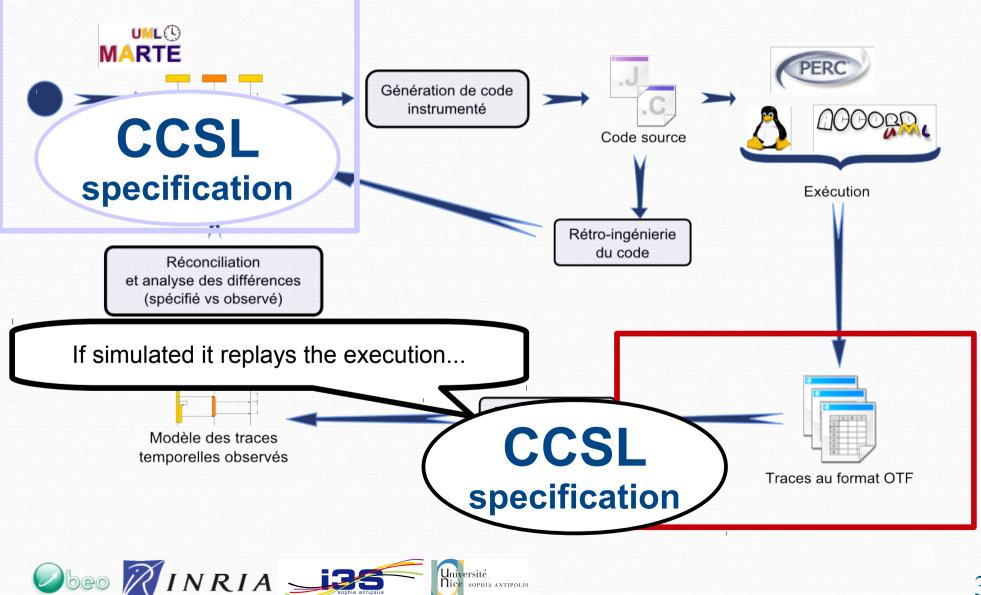

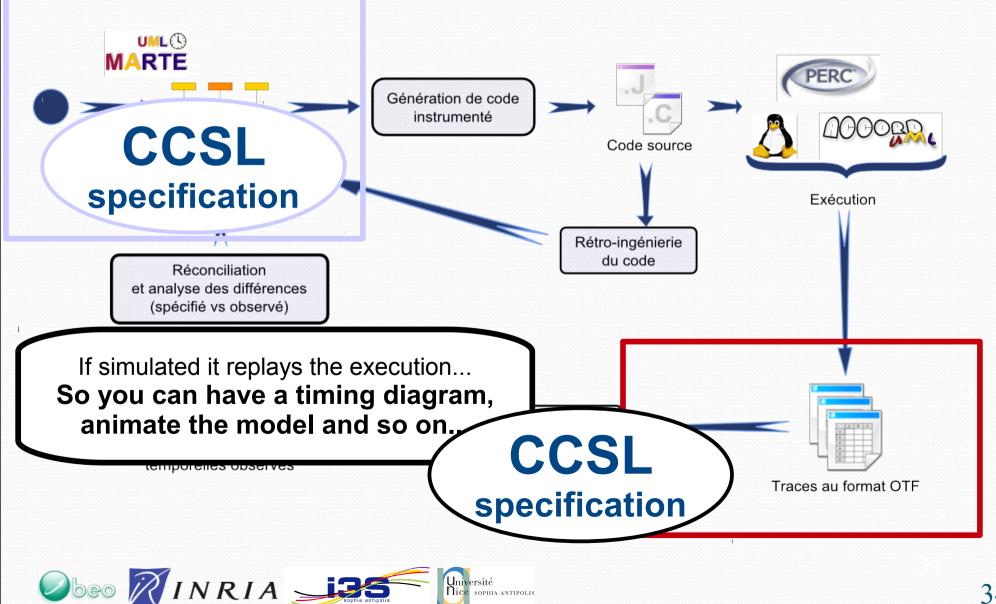

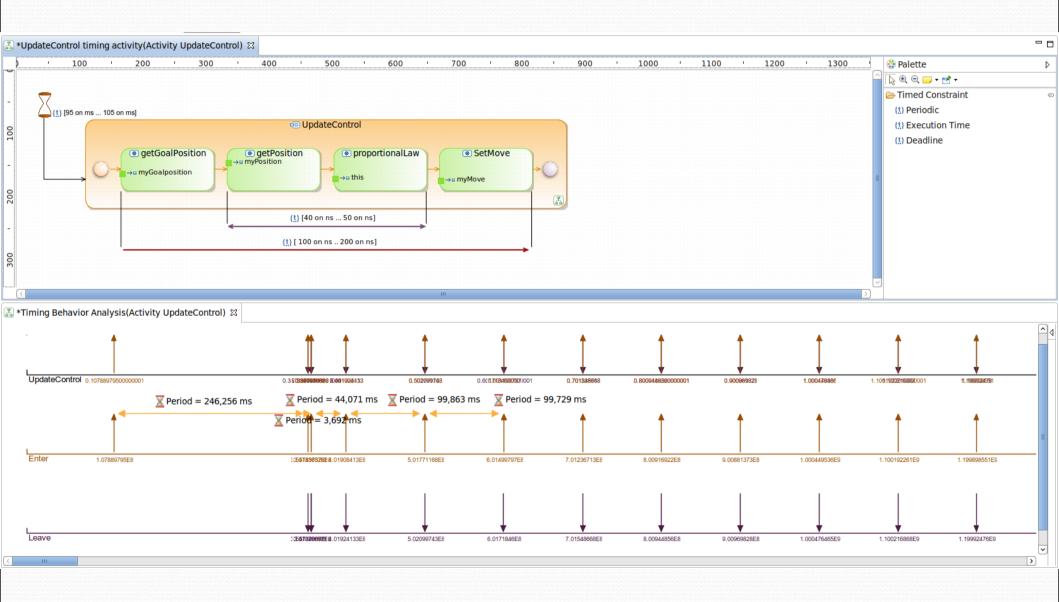

## Graphical formal annotation over a UML model for RT-Simex...

#### Simulate and animate the UML/MARTE model in TimeSquare

#### (http://www-sop.inria.fr/aoste/dev/time\_square/)

#### Simulate and animate the UML/MARTE model in TimeSquare

(http://www-sop.inria.fr/aoste/dev/time\_square/)

SOPHIA ANTIPOLIS

SOPHIA ANTIPOLIS

SOPHIA ANTIPOLIS

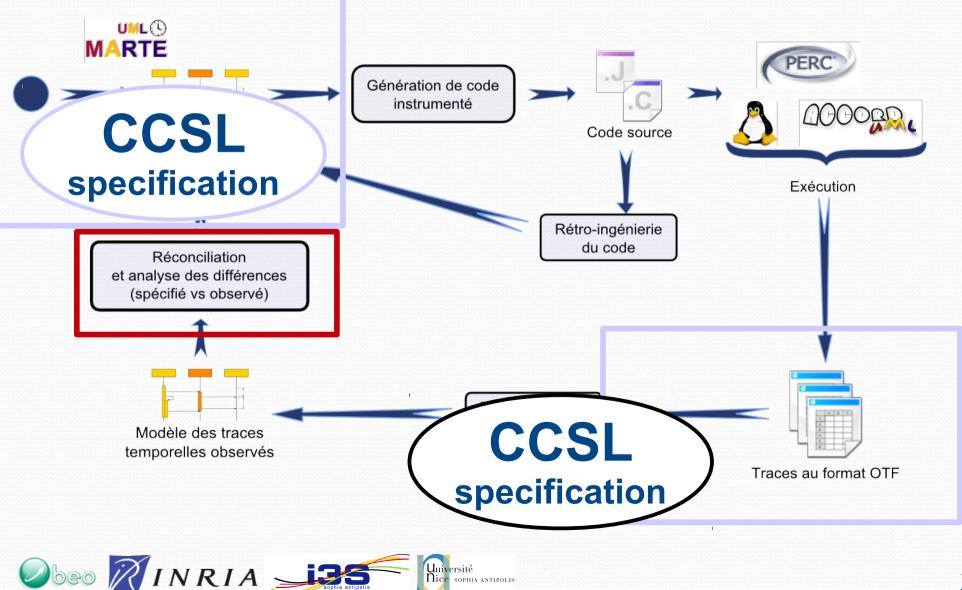

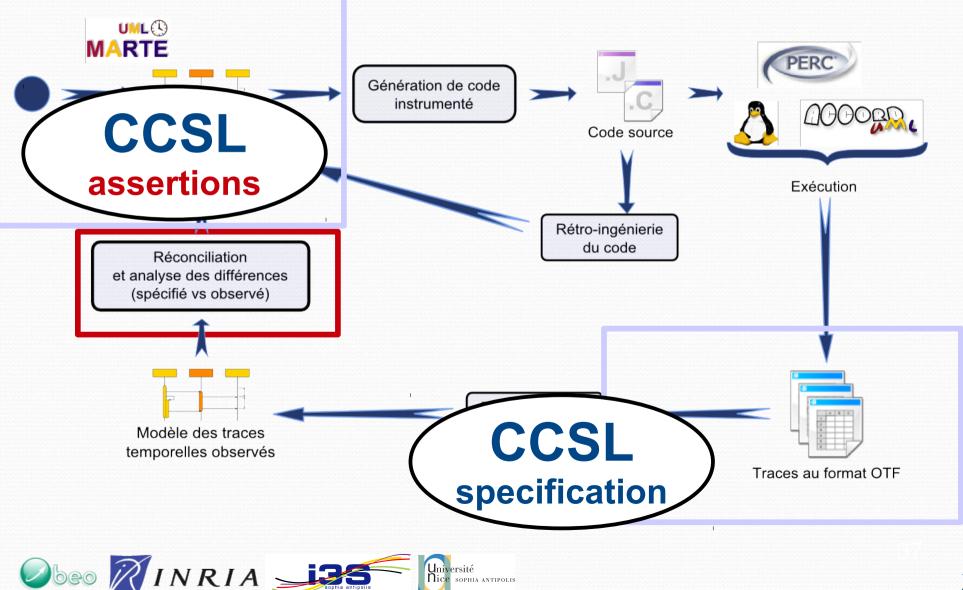

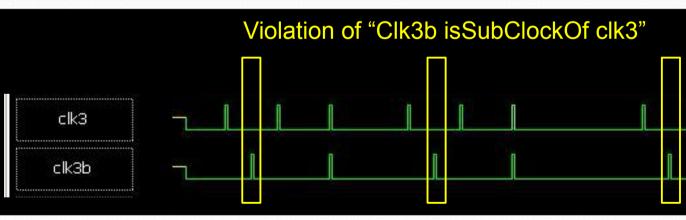

#### A specification and the actual execution

## You can simulation both together to see if a violation occurs

## You can simulation both together to see if a violation occurs

## Conclusion

## Conclusion

- Logical Time, via Marte and CCSL is used for

- The specification the expected behaviour

- The simulation at the model level of this behaviour

- The simulation at the model level of the actual behaviour (as monitored during the execution)

- The comparison between the specified and the actual behaviour