# Application Architecture Adequacy through an FFT case study

### Emilien Kofman - Jean-Vivien Millo - Robert de Simone AOSTE team, COMRED research unit

## 7th Junior Researcher Workshop on Real-Time Computing **RTNS** 2013

October 15, 2013

## **Motivations** - Modeling - Limitations

Problem: Weak portability for a given application.

AAA:

AAA requires a description of the HW (memory hierarchy, interconnect, computing elements, ...).

**Q RTNS** 2013

## **Motivations** - Modeling - Limitations

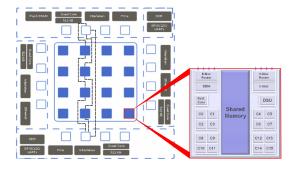

Kalray MPPA256

- Networks on chips replace/complement buses (for scalability purposes).

- Many different NoC based platforms exist.

- GPUs and CPUs have heterogeneous programming models NS 2013

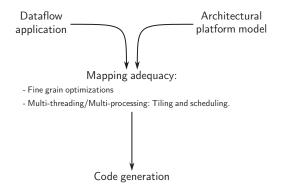

Required steps for AAA:

- **Dataflow SW modeling**: architecture independent

- e Hardware modeling

- **§** Fine grain adaptation (ILP) for each computation unit

- **3** Tiling and mapping coarse grain parallelism

- **Scheduling** computation and communication

## **Motivations - Modeling SW - Limitations**

#### Dataflow process networks: fine grain parallelism

4-samples FFT Data Flow representation

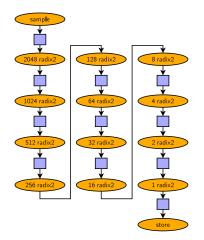

## **Motivations - Modeling SW - Limitations**

Dataflow process networks: coarse grain parallelism

Coarse 4096-samples FFT Data Flow representation

**W RTNS** 2013

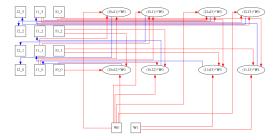

## **Motivations - Modeling SW - Limitations**

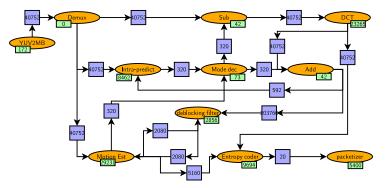

Dataflow process networks: refined application

H264 encoding annotated Data Flow representation

**W RTNS** 2013

## Motivations - Modeling HW - Limitations

#### • Sparse compiler parameters: streamlt

- Sparse code annotation: openMP (nb of threads), openCL (clDevice class), cuda (cudaDeviceProp structure).

- High level descriptions: sysML, TLM systemC

- Very accurate descriptions: Cycle Accurate Bit Accurate SystemC

- Synthesizable descriptions: HDL languages

AAA requires a hardware description: nb of threads and which address space they share, cache sizes, nb of DMA engines, throughput/latency/routing of the **interconnect**.

The AAA methodology is required for efficient design ans portability.

**Going further**: Consider all non-functional properties (Temperature/Power/Performance).

**Limitations**: It is much harder to model dynamic behaviors with dataflow process networks (data-dependent execution, temperature/power thresholds). HOPE (Hierarchically Organized Power/Energy management).

http://anr-hope.unice.fr/.