# M2 Digital Microelectronics

#### Contents

```

C1: Architecture des ordinateurs - niveau 2

Gestion des interruptions

Mémoire, caches

Unité de traitement, pipeline

Architectures RISC, super-scalaires, spécialisées

C2: Programmation d'architectures spécialisées (micro-contrôleurs, DSP)

Applications: traitements du signal et commande

C3: Conception de VLSI

Synthèse VHDL

Synthèse algorithmique

Placement/Routage (ASIC, FPGA)

Analyse de performances (vitesse, consommation, surface, ...)

C4: Architecture logicielle et matérielle (cosimulation)

Principe et étude de cas

```

#### Labs.

- · Programmation Pentium (C et assembleur)

- Programmation machine RISC (MIPS)

- Programmation DSP (TMS320C6711)

- · Synthèse VHDL

- · Architecture logicielle/matérielle

# Computer organization

### Chapters

- · CPU

- · Memory, cache

- · Pipe-line

- · Risc, Super-scalar, ...

- · DSP

#### L3 (Reminder)

# Notation pour la sémantique

| ichier |                 | Outils Affichage Fenêtre ?     |                                        | _                           |

|--------|-----------------|--------------------------------|----------------------------------------|-----------------------------|

|        |                 | →                              |                                        |                             |

|        | Notation        | Signification                  | Exemple                                | Signification               |

|        | $\leftarrow$    | Transfert de données. La       | $Reg[R1] \leftarrow$                   | Transfère le contenu du     |

|        |                 | longueur est donnée par la     | Reg[R2]                                | registre R2 dans le reg-    |

|        |                 | longueur de la destination.    |                                        | istre R1                    |

|        | $\leftarrow_n$  | Transfère $n$ bits. Permet     | $\texttt{Mem[y]} \leftarrow_{16}$      | Transfère 16 bits à par-    |

|        |                 | de lever l'ambiguïté sur la    | Mem[x]                                 | tir de la case mémoire x    |

|        |                 | longueur.                      |                                        | vers la case y.             |

|        | $X_n$           | Sélection du bit d'indice $n$  | $\text{Reg}[\text{R1}]_0 \leftarrow 0$ | Mise à 0 du bit 0 du reg-   |

|        |                 |                                |                                        | istre R1                    |

|        | $X_{mn}$        | Sélection d'un champ de        | $Reg[R3]_{70} \leftarrow$              | Transfère le contenu de     |

|        |                 | bits.                          | Mem[x]                                 | la case mémoire x dans      |

|        |                 |                                |                                        | l'octet bas de R3           |

|        | $X^n$           | Duplication d'un champ, n      | $Reg[R3]_{318} \leftarrow$             | Met à 0 les trois octets de |

|        |                 | fois.                          | $0^{24}$                               | poids fort de R3            |

|        | ##              | Concatène deux champs.         | Reg[R3] ←                              | Registre R3 reçoit le       |

|        |                 |                                | $0^{24}$ ##Mem[x]                      | contenu de la case          |

|        |                 |                                |                                        | mémoire x dans l'octet      |

|        |                 |                                |                                        | bas et 0 dans les 3 autres  |

|        |                 |                                |                                        | octets                      |

| F      | 200% ▼     4 28 | sur 28 ▶ 월 209,9 x 297 mm 월, 4 |                                        |                             |

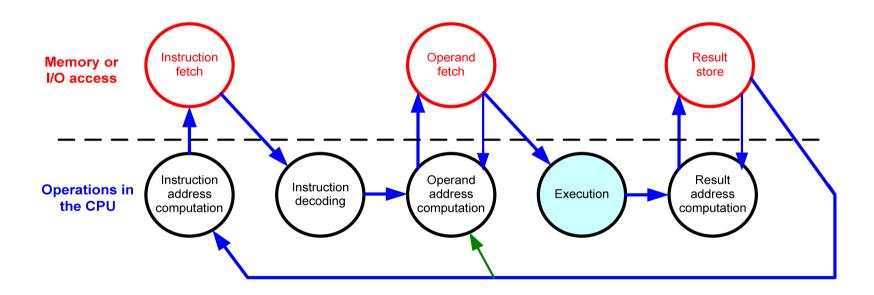

## Instruction Cycle